# Enhanced Device Performance of Germanium Nanowire Junctionless (GeNW-JL) MOSFETs by Germanide Contact Formation with Ar Plasma Treatment

Young Gwang Yoon,<sup>†</sup> Tae Kyun Kim,<sup>†</sup> In-Chan Hwang,<sup>‡</sup> Hyun-Seung Lee,<sup>‡</sup> Byeong-Woon Hwang,<sup>†</sup> Jung-Min Moon,<sup>†</sup> Yu-Jin Seo,<sup>†</sup> Suk Won Lee,<sup>†</sup> Moon-Ho Jo,<sup>§</sup> and Seok-Hee Lee<sup>\*,†</sup>

<sup>†</sup>Department of Electrical Engineering, Korea Advanced Institute of Science and Technology (KAIST), 373-1 Guseong-dong, Yuseong-gu, Daejeon 305-701, Republic of Korea

<sup>‡</sup>Department of Materials Science and Engineering, Pohang University of Science and Technology (POSTECH), San 31 Hyoja-Dong, Nam-gu, Pohang, Gyeongbuk 790-784, Republic of Korea

<sup>§</sup>Department of Materials Science and Engineering, Yonsei University, 50 Yonsei-ro, Seodaemun-gu, Seoul, 120-749, Republic of Korea

**Supporting Information**

**ABSTRACT:** In this study, germanium nanowire junctionless (GeNW-JL) metal-oxide-semiconductor-field-effect-transistors (MOSFETs) exhibited enhanced electrical performance with low source/drain (S/D) contact resistance under the influence of Ar plasma treatment on the contact regions. We found that the transformation of the surface oxide states by Ar plasma treatment affected the S/D contact resistance. With Ar plasma treatment, the germanium dioxide on the GeNW surface was effectively removed and increased oxygen vacancies were formed in the suboxide on the GeNW, whose germanium-

enrichment surface was obtained to form a germanide contact at low temperature. After a rapid thermal annealing process, Nigermanide contacts were formed on the Ar-plasma-treated GeNW surface. Ni-germanide contact resistance was improved by more than an order of magnitude compared to that of the other devices without Ni-germanide contact. Moreover, the peak field effect mobility value of the GeNW-JL MOSFETs was dramatically improved from 15 cm<sup>2</sup>/(V s) to 550 cm<sup>2</sup>/(V s), and the  $I_{on/off}$ ratio was enhanced from 1 × 10 to 3 × 10<sup>3</sup> due to Ar plasma treatment. The Ar plasma treatment process is essential for forming uniform Ni-germanide-contacts with reduced time and low temperature. It is also crucial for increasing mass productivity and lowering the thermal budget without sacrificing the performance of GeNW-JL MOSFETs.

KEYWORDS: GeNW-JL, MOSFETs, Ar plasma treatment, GeO<sub>2</sub>, suboxide, germanide contact

# INTRODUCTION

Germanium is a promising semiconductor material suitable for switching devices of integrated logic circuitry because of its high intrinsic mobility and compatibility for integration on Si complementary-metal-oxide-semiconductor (CMOS) technology. Various groups have recently investigated germanium electronics in efforts to realize devices with low voltage operation and high performance characteristics by source/drain (S/D) contact engineering<sup>1</sup> and interface passivation<sup>2</sup> between a semiconductor and gate insulator. As CMOS devices are being scaled down to match the sub-20 nm design rule, ultra-shallow and abrupt junction formation is essential for reducing short channel effects (SCEs).<sup>3</sup> Junction formation within this nanometer scale raises a degree of difficulty in the integration process and machining for the fabrication of high performance systems.

Recently, as one of the solutions to the issues related to junction technology, junctionless metal-oxide-semiconductor field-effect transistors (MOSFETs) were proposed and demonstrated based on a silicon-on-insulator (SOI) wafer for the first time.<sup>4,5</sup> Their desirable characteristics include a simple fabrication process,<sup>5,6</sup> low junction leakage,<sup>5</sup> bulk conduction,<sup>7</sup> a low transverse electric field,<sup>4,7</sup> and immunity to short channel effects (SCE).<sup>4,6</sup> However, S/D resistance degradation is the most critical problem of junctionless MOSFETs, without additional implantation on the S/D region.<sup>8</sup>

A cleaning process is conventionally a critical step in semiconductor manufacturing.<sup>9</sup> In particular, surface preparation of germanium before depositing the S/D metal onto contact holes is imperative for the purpose of removing the native oxide formed in the air ambient and chemisorption of water molecules.<sup>10–12</sup> Different groups have investigated various surface preparation methods conducted prior to epitaxial growth

Received:September 16, 2013Accepted:February 19, 2014Published:February 19, 2014

on the germanium substrate to make a clean and adhesive surface.<sup>9,13,14</sup> In particular, wet cleaning processes have been widely employed to remove the surface oxide, using halogen acid solutions such as diluted HF, HCl, HBr, and HI in Si technology.<sup>15–17</sup> However, in the case of germanium, a suboxide (GeO<sub>x</sub>, x < 2) remains even after pretreatment using a chemical solution, because oxidants contained in the solution cannot oxidize GeO<sub>x</sub> sufficiently to convert it into water-soluble GeO<sub>2</sub>.<sup>10,18</sup>

At roughly 400 °C above the desorption temperature, an annealing method to remove the  $\text{GeO}_x$  from the germanium surface consumes the germanium by growing  $\text{GeO}_2$  at the interface.<sup>10,19,20</sup> During the annealing process, desorption of GeO (g) also occurs and this can degrade the electrical properties.<sup>21,22</sup> It is thus necessary to develop a new technique to remove the surface oxide without consuming the germanium at low temperature to avoid the reaction mentioned above. To make high-performance GeNW-MOSFETs, surface treatment on the contact region of the oxidized germanium nanowire is essential, but very few studies have been done regarding its influence on electrical characteristics. Ar plasma treatment and its influences on electrical characteristics has not yet been reported.

In this work, germanium nanowire-based JL MOSFETs were compared to previously reported germanium plate-based JL MOSFETs<sup>23</sup> using a germanium-on-insulator (Ge–OI) wafer. Our devices exhibited improved performance compared to those reported in the literature.<sup>23</sup> By Ar plasma treatment, a cleaned and reactive germanium surface was obtained to form germanide-contacts at low temperature. Germanide-contacts reduced the contact resistance and enhanced the current drivability at low voltage.

### EXPERIMENTAL PROCEDURE

We synthesized single-crystal germanium nanowires by the vaporliquid-solid (VLS) method<sup>24–26</sup> using Au catalytic particles as a seed material. Au colloidal nanoparticles of 20 nm diameter were dispersed on SiO<sub>2</sub>/Si (100), and were loaded in a chemical-vapor-deposition (CVD) chamber. For an intrinsic single-crystalline germanium nanowire, premixed germane gas in H<sub>2</sub> (GeH<sub>4</sub>:H<sub>2</sub> = 1:10) was used as a precursor and nanowire growth was conducted under working pressure of 300 Torr and temperature of 310 °C for 5 min. For in situ ptype doping of germanium nanowire, premixed diborane gas (B<sub>2</sub>H<sub>6</sub>) in H<sub>2</sub> was subsequently injected to the same chamber and doped under working pressure of 10 Torr and temperature of 250 °C for 3 min.

One-hundred-nanometer-thick thermal oxide was grown on a heavily doped n-type silicon substrate as the bottom gate structure of junctionless MOSFETs, and the oxide at the bottom side of the wafer was removed by application of diluted hydrofluoric acid (HF:DI = 1:30) for 12 min followed by conventional cleaning. The top side of the grown thermal oxide acts as a gate insulator of the junctionless MOSFETs. To prepare Cr/Au pad metal deposited by an evaporator, we conducted photolithography and a lift-off process. Samples with the grown germanium nanowires were mixed with an IPA solution and agitated by an ultrasonic system to separate the germanium nanowires from the starting substrate. The germanium nanowires separated from the substrate were dispersed onto the top of a SiO<sub>2</sub>/Si substrate. To make S/ D contacts with Ni/Au (20 nm/70 nm) deposited by an evaporator, we carried out e-beam lithography and a lift-off process. After the e-beam photoresist was patterned, the following cleaning process steps were carried out. First, the sample was dipped into diluted hydrofluoric acid (HF:DI = 1:50) and into a deionized water (DI) solution three times respectively for 1 min. Second, Ar plasma treatment was performed by an inductively-coupled-plasma (ICP) system to introduce ion bombardment onto the Ge-NW surface under a working pressure below 1 mTorr. Ar-treated samples were exposed in the air within 10 s and subsequently shifted to the vacuum chamber of the evaporator. After Ni/Au

deposition, a thermal annealing process was executed in a rapid thermal annealing (RTA) system under 320  $^\circ C$  for 30 s.

## RESULTS AND DISCUSSION

Figure 1a shows a scanning-electron-microscope (SEM) image of GeNWs grown by CVD at 310  $^\circ\text{C}$  on a SiO\_/Si substrate.

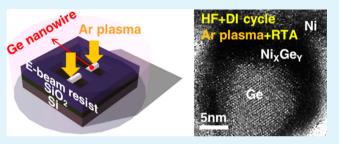

**Figure 1.** (a) SEM image of germanium nanowire grown by CVD on the  $SiO_2/Si$ . (b) Schematic diagram of the dispersed GeNW on  $SiO_2/Si$  substrate. (c) Schematic diagram of S/D patterned with e-beam resist by e-beam lithography. Opened S/D area was processed with various surface treatments: (I) reference sample, (II) HF+DI cycle sample, (III) Ar plasma treatment sample, (IV) HF+DI cycle+Ar plasma treatment sample. (d) Top view of SEM image of fabricated p-type Ge-NW JL MOSFET.

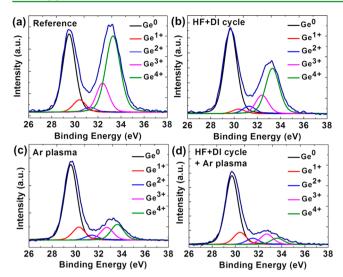

Figure 1b shows a schematic diagram of the dispersed germanium nanowires on SiO<sub>2</sub>/Si substrate. Figure 1c shows a schematic diagram of S/D patterned with e-beam resist by ebeam lithography. The opened S/D region was processed with various surface treatments ((I) reference sample, (II) HF+DI cycle sample, (III) Ar plasma treatment sample, (IV) HF+DI cycle+Ar plasma treatment sample). Figure 1d shows the top view of a SEM image of a fabricated p-type GeNW-JL MOSFET. The intensity with respect to the binding energy was inspected by a X-ray Photoelectron Spectroscopy (XPS) system (Thermo Scientific, model MultiLab 2000) having a spherical sector analyzer and aluminum K $\alpha$  line with a photon energy of 1486.6 eV. All samples were loaded in an ultrahigh vacuum (UHV) of 5 x 10<sup>-10</sup> mbar. Ge nanowires grown on a SiO<sub>2</sub>/Si substrate were used as samples for XPS analyses, and these samples were investigated to confirm the effects of surface treatment such as wet HF+DI cycle and dry Ar plasma treatment processes. XPS spectra of the surface treated samples are shown in Figure 3 and Figure S1 in the Supporting Information, and the percentage ratio of the germanium and various germanium oxides are tabulated in Table S1 and Table S2 in the Supporting Information. Deconvoluted peaks are summarized in Figure 2 and Figure S2 in the Supporting Information. We have used the carbon peak (C1s =  $2\hat{85.4}$  eV) to calibrate all samples with a reference sample. To extract the peak areas of the germanium and various germanium oxides, XPS spectra were deconvoluted into five peak lines to fit the Ge3d spectra, corresponding to Ge  $(Ge^{0}), Ge_{2O} = O (Ge^{1+}), GeO (Ge^{2+}), Ge_{2O} = O_{3} (Ge^{3+}), and GeO_{2}$  $(Ge^{4+})$ .<sup>27–29</sup> The main peak of Ge3d appeared at 29.7 eV, which

**Figure 2.** Ge3d peak spectra of the germanium and germanium oxides in various surface treatment conditions. (a) Reference sample (as-grown sample, air-exposed without any surface treatment), (b) HF+DI cycle sample, (c) Ar plasma treatment sample, (d) HF+DI cycle + Ar plasma treatment sample.

is related to Ge<sup>0</sup>, and the core-level shifts of the various oxidation states levels were consistent with those in the literature reported for a Ge wafer.<sup>29</sup> The full width at half maxima (FWHMs) of all samples were fixed at a value of 1.4 eV, and the fitting method of all samples was based on a combination of Gaussian and Lorentzian with a ratio of 7:3.<sup>29</sup>

To investigate the oxide removal effect of our surface treatment methods, we started with a reference sample having 41.3 percent (%) GeO<sub>2</sub> on the nanowire surface, which was confirmed by deconvolution of the XPS spectra, as shown in Table S1 in the Supporting Information. Figure 2a shows that the  $GeO_2$  (Ge<sup>4+</sup>) peak intensity of the reference sample (as-grown sample, air-exposed without any surface treatment) is higher than the summation of the germanium suboxides ( $Ge^{1+}$ ,  $Ge^{2+}$ , and  $Ge^{3+}$ ) intensity, indicating that germanium nanowires of reference sample were dominantly encapsulated with germanium dioxide. GeO<sub>2</sub> peak of the sample treated with HF+DI cycle is lower than that of the reference sample and the difference in the germanium suboxide ( $Ge^{1+}$ ,  $Ge^{2+}$ , and  $Ge^{3+}$ ) summation is below 3 % (see Table S1 in the Supporting Information). This indicates that GeO<sub>2</sub> was etched during the HF+DI cycle treatment because of properties of the germanium oxide, which reacted with fluoride and the aqueous solution.<sup>10,15</sup>

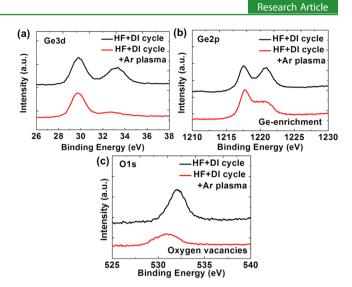

As shown in Figure 3a, with Ar plasma treatment, GeO<sub>2</sub> was reduced by more than 15% and the suboxide summation was increased by more than 9% compared to the HF+DI cycle sample. This indicates that Ar plasma treatment breaks bonds in GeO<sub>2</sub>, changing compositions toward suboxides. The composition-altered surface layer of the Ar treated sample was thus dominantly composed of suboxide such as Ge<sub>2</sub>O<sub>3</sub> and Ge<sub>2</sub>O after removing the GeO<sub>2</sub>. Peak broadening of the oxide component is clearly shown in Figure 3b and this is ascribed to the higher surface sensitivity of the Ge2p electrons.<sup>18</sup>

As shown in Figure 3c, higher oxidation states were removed and lower oxidation states were formed at the nanowire surface by Ar ion bombardment, as confirmed by peak broadening and a chemical shift to the lower binding energy side in the XPS spectra. The atomic percentage of oxygen in the Ge–O bond was reduced from 60 to 45 with Ar plasma treatment (see Table S2 in

**Figure 3.** (a) Ge3d core-level spectra without and with Ar plasma treatment. (b) Ge2p core-level spectra without and with Ar plasma treatment. (c) O1s core-level spectra without and with Ar plasma treatment.

the Supporting Information), indicating that oxygen deficiency is increased due to preferential sputtering of oxygen. With Ar plasma treatment only, a chemical shift occurs to the lower binding energy side, resulting in an atomic percentage reduction of oxygen in the Ge–O bond, consistent with previous results.

As shown in Table S3 in the Supporting Information, the nonstoichiometric ratio of Ge3d and O1s was due to a mixed germanium suboxide on the nanowire surface. With Ar plasma treatment, the ratio was changed to a Ge-enrichment state. As in the preceding XPS data results, Ge-enrichment occurs as shown in the EELS spectrum, which was obtained to verify the state of the interface oxide.<sup>30–32</sup> In the case of p-type germanium nanowire, when the oxide was completely eliminated from the nanowire surface by high-temperature thermal annealing, the Ge<sup>0</sup>3d peak was shifted from 29.8 to 29.5 because of recovery of band bending at the surface between the germanium and germanium oxide.<sup>33</sup> However, with Ar plasma treatment, the Ge<sup>0</sup> peak was not shifted to lower binding energy in the Ge3d spectra.

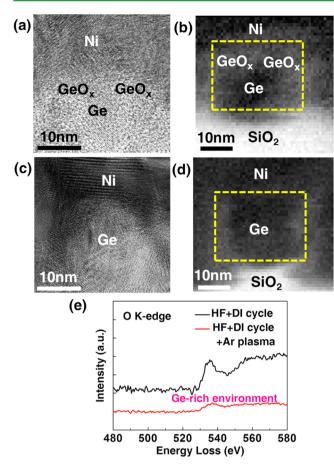

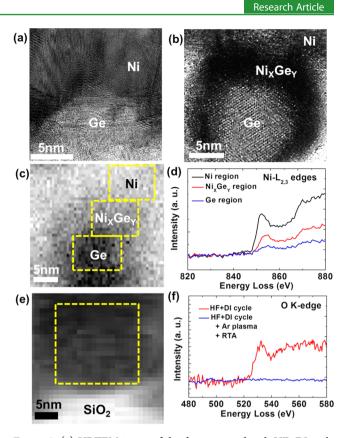

Germanium oxide existed at the interface between the S/D metal and the germanium nanowire, which was confirmed by the peak of the localized oxygen K edge arising from O-O scattering at around 530 eV,<sup>34</sup> and this peak decreased as the number of O second-nearest neighbors around the excited O atoms decreased.<sup>35</sup> As shown in Figure 4a HRTEM image of HF+DI cycle sample, one can distinguish amorphous GeO<sub>2</sub> region from Ge crystalline region. The result from oxygen map image of Figure 4b was consistent with HRTEM image. But, the interface between Ni and Ge nanowire of the Ar-treated device after the HF+DI cycle was crystallized as shown in Figure 4c. This result from oxygen map image of Figure 4d was strikingly different from that of Figure 4b. EELS spectra were extracted from area region marked on panels b and d in Figure 4. As shown in Figure 4e, the difference in intensities between the nontreated sample and the Ar-treated sample at around 530 eV was due to reduced O atoms. The reduced peak, shown in Figure 4e, indicates that more O second-nearest neighbors are missing, resulting in a Ge enrichment environment.35

High-resolution transmission electron microscopy (HR-TEM), scanning transmission electron microscopy (STEM), and energy-dispersive spectroscopy (EDS) were conducted to

## **ACS Applied Materials & Interfaces**

**Figure 4.** (a) HRTEM image of HF+DI cycle-treated device. (b) EELS oxygen map of HF+DI cycle-treated device. (c) HRTEM image of HF+DI cycle+Ar plasma-treated device. (d) EELS oxygen map of HF+DI cycle+Ar plasma-treated device. (e) EELS spectra of germanium nanowire without and with Ar plasma treatment after HF+DI cycle.

verify germanide-contact formation.<sup>36</sup> Because  $\text{GeO}_x$  converts to  $\text{GeO}_2$  above 400 °C, germanium will be consumed as oxide grows on the surface.<sup>10</sup> The thermal process conditions were thus fixed below 400 °C.

HF+DI cycle-only samples were compared to Ar-treated sample in order to study the effects of Ge enrichment of the nanowire surface on germanide contact formation after the thermal annealing process. In the HF+DI cycle sample case, as shown in Figure 5a, Ni-germinide contact was not formed at the germanium nanowire surface because of the unremoved surface oxide, which blocked the nickel diffusion. This means that, at low temperature, diffusion was retarded because of the absence of atom diffusion paths such as dislocation sites and grain boundaries.<sup>37</sup> However, as shown in Figure 5b, a germanide contact was successfully formed at the surface of GeNW treated with Ar plasma; this is ascribed to the high density of oxygen vacancies in the Ge enrichment environment. As shown in panels c and d in Figure 5, nickel and germanium were intermixed at the surface of nanowire, indicating that amorphous Ni<sub>x</sub>Ge<sub>y</sub> germanide was formed at the surface of nanowire. As shown in panels e and f in Figure 5, the sample treated with HF+DI cycle +Ar plasma treatment and annealed at 320 °C has no oxygen at the interface between germanium and nickel. Diffusion of Nimetal to germanium is much more dependent on vacancy mediation than in the case of silicon, suggesting that Ni-metal can effectively diffuse through the series of vacant cations and oxygen

**Figure 5.** (a) HRTEM image of the device treated with HF+DI cycle and annealed at 320 °C (b) HRTEM image of the device treated with HF+DI cycle+Ar plasma treatment and annealed at 320 °C. (c) EELS nickel map of the device treated with HF+DI cycle+Ar plasma treatment and annealed at 320 °C. (d) EELS spectra of the device treated with HF +DI cycle+Ar plasma treatment and annealed at 320 °C with various marked region : Ni region, Ni<sub>X</sub>Ge<sub>Y</sub> region, Ge region. (e) EELS oxygen map of the device treated with HF+DI cycle+Ar plasma treatment and annealed at 320 °C. (f) EELS spectra comparison.

can diffuse out through the vacancy sites, leading to the formation of uniform Ni-germanide contact (see Figures S4 and S5 in the Supporting Information).<sup>34</sup> Uniform germanide contact is required to prevent saturation of the allowed density of states (DOS), which is one of the main factors limiting carrier transport in nanometer-range contact.

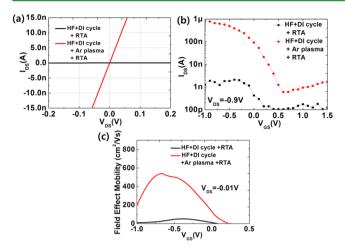

The performance of different GeNW-JL MOSFETs is compared to verify the effects of the Ar plasma treatment on contact resistance and device characteristics, which were measured by a semiconductor device analyzer (Agilent Technologies, model B1500). The channel length and nanowire diameters of all devices were fixed at 3  $\mu$ m and 15 nm, respectively, as shown in Figures 1d and 5b. It was found that the sum of resistance  $R_{\rm CH} + R_{\rm SD}$  is equal to 3.8 M $\Omega$  ( $V_{\rm GS} = 0$  V) after the thermal process at 320 °C. Before germanide contact formation, the resistance values were more than an order of magnitude higher compared to the Ar-treated device, as shown in Figure 6a.

In the off-state operation region ( $V_{\rm GS} = 0$  V) of junctionless MOSFETs, the channel resistance is dominant due to depleted charges in the channel region resulting from band bending at the narrow germanium channel region due to the work function difference between the channel and the gate electrode.<sup>38</sup> However, before annealing, the resistance  $R_{\rm SD}$  is dominant, thereby leading to pA range current at  $V_{\rm DS} = -0.2$  V. When the channel is formed in the on-state ( $V_{\rm GS} \approx -2$  V >  $V_{\rm TH}$ ), the S/D

**Figure 6.** (a) Two-terminal electrical characteristics of the devices without and with Ar plasma treatment. (b) Transfer characteristics of the devices without and with Ar plasma treatment. (c) Field effect mobility of the devices without and with Ar plasma treatment.

contact resistance is the dominant factor limiting the carrier transport, by neglecting the channel resistance due to the highly doped channel in junctionless MOSFETs. During the on-state, the resistance  $R_{\text{CH}} + R_{\text{SD}}$  was below 420 k $\Omega$ ; this low value is due to recovery of depleted charges in the channel region.<sup>5</sup>

From the transfer characteristics shown in Figure 6b, it was found that the threshold voltage of the untreated device was higher and the on-off current ratio was lower relative to the Artreated device, suggesting that charge transport characteristics through the contact regions were dramatically improved by the germanide-contact due to Ar plasma treatment. Ge-NW MOSFETs exhibited a subthreshold voltage swing of 110 mV/ decade, threshold voltage of a -0.2 V, and on-off current ratio of  $3 \times 10^3$ , and the gate leakage current was maintained below the off-state current through the whole region of device operation. The threshold voltage was extracted from constant drain current of 200 nA.

To extract the field effect mobility, the capacitance was extracted by a cylinder-on-plate model,<sup>39</sup> and the field effect mobility of bottom gate Ge-NW JL MOSFETs was extracted from FET characteristics reported in the literature.<sup>39</sup> As shown in Figure 6c, the peak of the field effect mobility in the linear operation region was 550  $\text{cm}^2/(\text{V s})$ . At the saturation region  $(V_{\rm DS} = -0.9 \text{ V})$ , the gate drivability is higher than that reported in the literature<sup>23,40</sup> in terms of the subthreshold voltage slope and the threshold voltage for low power operation. Ge-NW JL MOSFETs were successfully demonstrated for the first time, and the on current normalized by the diameter of the nanowire (divided by  $\pi \times$  diameter) was 17  $\mu$ A/ $\mu$ m, which is also higher than the values in the literature.<sup>23,40</sup> The p-type doping level in Ge-NW can be obtained from the relation between resistivity and mobility, corresponding to a doping level close to  $4 \times 10^{18}$  cm<sup>-3</sup>. Output characteristics of the treated device and the resistance of the channel were well modulated by an order of magnitude (see Figure S6c in the Supporting Information).

In junctionless transistors, the difference between the gate electrode work function and the fermi level of the channel material can affect the off current characteristics of the devices and the subthreshold-voltage slope. Thus, a highly n-type doped Si wafer was used to achieve a low work function to reduce the off current and to control the threshold voltage for high quality junctionless transistor operation.<sup>4–6</sup> The subthreshold-voltage

swing of the devices was optimized by shrinking the gate insulator thickness, and the off current was also reduced by avoiding the voltage drop across the oxide, achieving band bending of the germanium nanowires to deplete holes in the channel region.

The reason the GeNW JL MOSFETs are well-designed to deplete holes in the channel and reduce the off current, is based on a relation that can be found in the literature.<sup>23</sup> As a result of shrinking the oxide thickness channel length and using a multinanowire scheme, Ge-NW JL MOSFETs are a promising candidate for low-power and high-performance integrated logic circuits.

### SUMMARY AND CONCLUSION

In summary, we demonstrated germanium nanowire-based junctionless (GeNW-JL) MOSFETs and they exhibited improved performance compared to devices without Ar plasma treatment. In addition, we investigated the effects of Ar plasma treatment on chemical properties of the germanium nanowire surface and the electrical properties of the S/D contact region. As a result of effective treatment for oxygen vacancies and a Ge enrichment environment at the surface, the contact resistance of the Ar plasma-treated device was reduced by more than an order of magnitude after thermal processing at low temperature. This achievement resulted from uniform germanidation between the nickel and germanium nanowire surface. Enhanced device performance including peak field-effect mobility of 550 cm<sup>2</sup>/(V s), an  $I_{on/off}$  ratio of  $3 \times 10^3$ , a subthreshold-voltage-swing of 110 mV/decade, and enhancement mode operation with a threshold voltage of -0.2 V were thereby achieved. In conclusion, oxides such as GeO<sub>2</sub> and suboxides grown in the air ambient and regrown in solution can be effectively removed by Ar plasma treatment. This is a promising process because it can be carried out in a few minutes at low temperature, and it improves the S/D resistance between germanium nanowire and S/D electrodes. Our process is thus expected to be practically applied in preventing electrical characteristic degradation of GeNW-JL MOSFETs for future electronics.

#### ASSOCIATED CONTENT

#### **S** Supporting Information

XPS spectra of Ge3d, Ge2p, and O1s in various treatment conditions. XPS peak area percentages of Ge3d and O1s in various treatment conditions. HRTEM image and FFT of cross section of reference sample. EDS maps of devices treated in various conditions. Lateral and vertical profiles of the EDS maps of device treated with HF+DI cycle+Ar plasma treatment and thermal annealing. At various  $V_{\rm G}$  and  $V_{\rm D}$ , transfer and output characteristics of device treated with HF+DI cycle+Ar plasma treatment and thermal annealing. This material is available free of charge via the Internet at http://pubs.acs.org/.

#### AUTHOR INFORMATION

## **Corresponding Author**

\*E-mail: seokheelee@ee.kaist.ac.kr.

#### Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

This work was supported by the Center for Integrated Smart Sensors funded by the Ministry of Science, ICT & Future Planning as Global Frontier Project (CISS-2012054187)

#### **ACS Applied Materials & Interfaces**

## REFERENCES

(1) Zhang, Y. Y.; Oh, J.; Li, S. G.; Jung, S. Y.; Park, K. Y.; Shin, H. S.; Lee, G. W.; Wang, J. S.; Majhi, P.; Tseng, H. H.; Jammy, R.; Bae, T. S.; Lee, H. D. Ni Germanide Utilizing Ytterbium Interlayer for High-Performance Ge MOSFETs. *Electrochem. Solid-State Lett.* **2009**, *12*, H18–H20.

(2) Caymax, M.; Houssa, M.; Pourtois, G.; Bellenger, F.; Martens, K.; Delabie, A.; Van Elshocht, S. Interface Control of High-k Gate Dielectrics on Ge. *Appl. Surf. Sci.* **2008**, *254*, 6094–6099.

(3) Veeraraghavan, S.; Fossum, J. G. Short-Channel Effects in SOI MOSFETs. *IEEE Trans. Electron Devices* **1989**, *36*, 522–528.

(4) Lee, C. W.; Afzalian, A.; Akhavan, N. D.; Yan, R.; Ferain, I.; Colinge, J. P. Junctionless Multigate Field-Effect Transistor. *Appl. Phys. Lett.* **2009**, *94*, 053511–053511-2.

(5) Colinge, J. P.; Lee, C. W.; Afzalian, A.; Akhavan, N. D.; Yan, R.; Ferain, I.; Razavi, P.; O'Neill, B.; Blake, A.; White, M.; Kelleher, A. M.; McCarthy, B.; Murphy, R. Nanowire Transistors without Junctions. *Nat. Nanotechnol.* **2010**, *5*, 225–229.

(6) Ferain, I.; Colinge, C. A.; Colinge, J. P. Multigate Transistors as the Future of Classical Metal-Oxide-Semiconductor Field-Effect Transistors. *Nature* **2011**, *479*, 310–316.

(7) Colinge, J. P.; Lee, C. W.; Ferain, I.; Akhavan, N. D.; Yan, R.; Razavi, P.; Yu, R.; Nazarov, A. N.; Doria, R. T. Reduced Electric Field in Junctionless Transistors. *Appl. Phys. Lett.* **2010**, *96*, 073510–073510-3.

(8) Lee, C. W.; Ferain, I.; Afzalian, A.; Yan, R.; Akhavan, N. D.; Razavi, P.; Colinge, J. P. Performance Estimation of Junctionless Multigate Transistors. *Solid-State Electron.* **2010**, *54*, 97–103.

(9) Akane, T.; Tanaka, J.; Okumura, H.; Matsumoto, S. Preparation of High-Quality Ge Substrate for MBE. *Appl. Surf. Sci.* **1997**, *108*, 303–305.

(10) Kamata, Y. High-k/Ge MOSFETs for Future Nanoelectronics. *Mater. Today* **2008**, *11*, 30–38.

(11) Tabet, N.; Faiz, M.; Hamdan, N.; Hussain, Z. High Resolution XPS Study of Oxide Layers Grown on Ge Substrates. *Surf. Sci.* 2003, 523, 68–72.

(12) Ellis, S. Surface Studies on Single-Crystal Germanium. J. Appl. Phys. 1957, 28, 1262–1269.

(13) Moriyama, Y.; Hirashita, N.; Toyoda, E.; Usuda, K.; Nakaharai, S.; Sugiyama, N.; Takagi, S. I. Study of the Surface Cleaning of GOI and SGOI Substrates for Ge Epitaxial Growth. *ECS Trans.* **2006**, *3*, 1183– 1190.

(14) Moriyama, Y.; Hirashita, N.; Usuda, K.; Nakaharai, S.; Sugiyama, N.; Toyoda, E.; Takagi, S. I. Study of the Surface Cleaning of GOI and SGOI Substrates for Ge Epitaxial Growth. *Appl. Surf. Sci.* **2009**, *256*, 823–829.

(15) Onsia, B.; Conard, T.; De Gendt, S.; Heyns, M.; Hoflijk, I.; Mertens, P.; Meuris, M.; Raskin, G.; Sioncke, S.; Teerlinck, I.; Theuwis, A.; Steenbergen, J. V.; Vinckier, C. A Study of the Influence of Typical Wet Chemical Treatments on the Germanium Wafer Surface. *Solid State Phenom.* **2005**, *103*, 104–107.

(16) Morita, M.; Ohmi, T.; Hasegawa, E.; Kawakami, M.; Ohwada, M. Growth of Native Oxide on a Silicon Surface. *J. Appl. Phys.* **1990**, *68*, 1272–1281.

(17) Kern, W. The Evolution of Silicon Wafer Cleaning Technology. J. Electrochem. Soc. **1990**, 137, 1887–1892.

(18) Prabhakaran, K.; Maeda, F.; Watanabe, Y.; Ogino, T. Thermal Decomposition Pathway of Ge and Si Oxides: Observation of a Distinct Difference. *Thin Solid Films* **2000**, *369*, 289–292.

(19) Zhang, X. J.; Xue, G.; Agarwal, A.; Tsu, R.; Hasan, M. A.; Greene, J.; Rockett, A. Thermal Desorption of Ultraviolet–Ozone Oxidized Ge (001) for Substrate Cleaning. *J. Vac. Sci. Technol., A* **1993**, *11*, 2553–2561.

(20) Oh, J.; Campbell, J. C. Thermal Desorption of Ge Native Oxides and the Loss of Ge from the Surface. *J. Electron. Mater.* **2004**, *33*, 364–367.

(21) Prabhakaran, K.; Maeda, F.; Watanabe, Y.; Ogino, T. Distinctly Different Thermal Decomposition Pathways of Ultrathin Oxide Layer on Ge and Si Surfaces. *Appl. Phys. Lett.* **2000**, *76*, 2244–2246.

(22) Kamata, Y.; Kamimuta, Y.; Ino, T.; Nishiyama, A. Direct Comparison of  $ZrO_2$  and  $HfO_2$  on Ge Substrate in Terms of the Realization of Ultrathin High-Kappa Gate Stacks. *Jpn. J. Appl. Phys.* **2005**, 44, 2323–2329.

(23) Zhao, D. D.; Nishimura, T.; Lee, C. H.; Nagashio, K.; Kita, K.; Toriumi, A. Junctionless Ge p-Channel Metal–Oxide–Semiconductor Field-Effect Transistors Fabricated on Ultrathin Ge-on-Insulator Substrate. *Appl. Phys. Express* **2011**, *4*, 031302–031304.

(24) Lew, K. K.; Pan, L.; Dickey, E. C.; Redwing, J. M. Vapor–Liquid– Solid Growth of Silicon–Germanium Nanowires. *Adv. Mater.* **2003**, *15*, 2073–2076.

(25) Lew, K. K.; Pan, L.; Dickey, E. C.; Redwing, J. M. Effect of Growth Conditions on the Composition and Structure of  $Si_{1-x}Ge_x$  Nanowires Grown by Vapor–Liquid–Solid Growth. *J. Mater. Res.* **2006**, *21*, 2876–2881.

(26) Kodambaka, S.; Tersoff, J.; Reuter, M. C.; Ross, F. M. Germanium Nanowire Growth below the Eutectic Temperature. *Science* **2007**, *316*, 729–732.

(27) Hosoi, T.; Kutsuki, K.; Okamoto, G.; Saito, M.; Shimura, T.; Watanabe, H. Origin of Flatband Voltage Shift and Unusual Minority Carrier Generation in Thermally Grown GeO<sub>2</sub>/Ge Metal-Oxide-Semiconductor Devices. *Appl. Phys. Lett.* 2009, *94*, 202112-202112–3.

(28) Vijayarangamuthu, K.; Rath, S.; Kabiraj, D.; Avasthi, D. K.; Kulriya, P. K.; Singh, V. N.; Mehta, B. R. Ge Nanocrystals Embedded in a GeO<sub>x</sub> Matrix Formed by Thermally Annealing of Ge Oxide Films. *J. Vac.*

Sci. Technol, A 2009, 27, 731–733.

(29) Kai Wang, S.; Liu, H. G.; Toriumi, A. Kinetic Study of GeO Disproportionation into a GeO<sub>2</sub>/Ge System Using X-ray Photoelectron Spectroscopy. Appl. Phys. Lett. 2012, 101, 061907–061907-4.

(30) Rowe, J. Photoemission and Electron Energy Loss Spectroscopy of GeO<sub>2</sub> and SiO<sub>2</sub>. *Appl. Phys. Lett.* **1974**, *25*, 576–578.

(31) Chang, K.; Nuhfer, N.; Porter, L.; Wahab, Q. High-Carbon Concentrations at the Silicon Dioxide–Silicon Carbide Interface Identified by Electron Energy Loss Spectroscopy. *Appl. Phys. Lett.* **2000**, 77, 2186–2188.

(32) Lensch-Falk, J. L.; Hemesath, E. R.; Perea, D. E.; Lauhon, L. J. Alternative Catalysts for VSS Growth of Silicon and Germanium Nanowires. *J. Mater. Chem.* **2009**, *19*, 849–857.

(33) Wang, D.; Chang, Y. L.; Wang, Q.; Cao, J.; Farmer, D. B.; Gordon, R. G.; Dai, H. Surface Chemistry and Electrical Properties of Germanium Nanowires. *J. Am. Chem. Soc.* **2004**, *126*, 11602–11611.

(34) Muller, D. A.; Silcox, J. Delocalization in Inelastic Scattering. *Ultramicroscopy* **1995**, *59*, 195–213.

(35) Muller, D.; Sorsch, T.; Moccio, S.; Baumann, F.; Evans-Lutterodt, K.; Timp, G. The Electronic Structure at the Atomic Scale of Ultrathin Gate Oxides. *Nature* **1999**, *399*, 758–761.

(36) Iyota, M.; Yamamoto, K.; Wang, D.; Yang, H.; Nakashima, H. Ohmic Contact Formation on n-Type Ge by Direct Deposition of TiN. *Appl. Phys. Lett.* **2011**, *98*, 192108–192108-3.

(37) Wittmer, M. Barrier Layers: Principles and Applications in Microelectronics. J. Vac. Sci. Technol., A **1984**, *2*, 273–280.

(38) Rios, R.; Cappellani, A.; Armstrong, M.; Budrevich, A.; Gomez, H.; Pai, R.; Rahhal-Orabi, N.; Kuhn, K. Comparison of Junctionless and Conventional Trigate Transistors with  $L_g$  Down to 26nm. *IEEE Electron Device Lett.* **2011**, 32, 1170–1172.

(39) Wunnicke, O. Gate Capacitance of Back-Gated Nanowire Field-Effect Transistors. *Appl. Phys. Lett.* **2006**, *89*, 083102-083102–3.

(40) Zhao, D. D.; Lee, C. H.; Nishimura, T.; Nagashio, K.; Cheng, G. A.; Toriumi, A. Experimental and Analytical Characterization of Dual-Gated Germanium Junctionless p-Channel Metal-Oxide-Semiconductor Field-Effect Transistors. *Jpn. J. Appl. Phys.* **2012**, *51*, 04DA03-04DA03-7.